E8 262: CAD for High Speed Chip-Package-Systems (3:0)

Instructor: Dipanjan Gope

Term: Jan-Apr

Class Timings: Tues 18:00pm-19:30pm and Fri 07:30-09:00am

Class Venue: ECE 1.08

Lecture Notes

Web Discussion Forum

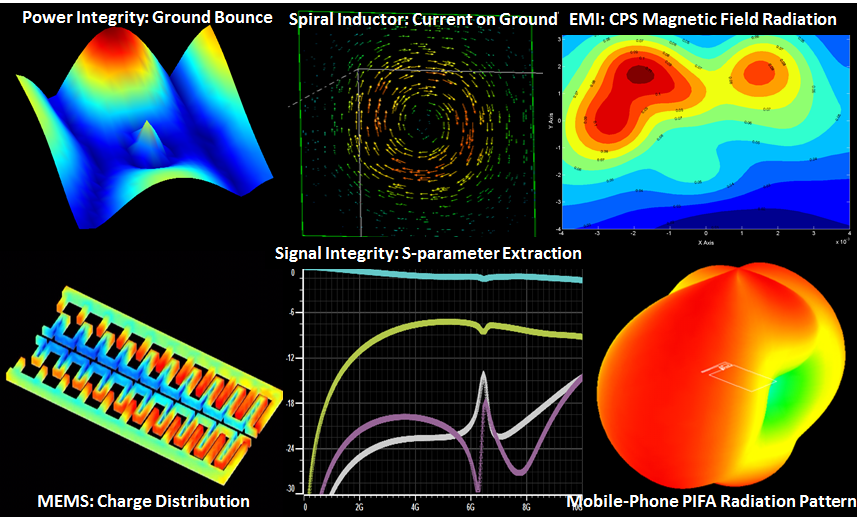

The objective of this course is to provide an exposure to fundamental numerical techniques used in modeling and simulation of high speed interconnects and power distribution networks as encountered in chip package systems.

Module 1: Electrical Challenges in High Speed Chip-Package-Systems

Module 1: Electrical Challenges in High Speed Chip-Package-Systems

- Types of packages and PCBs

- Packaging Trends

- Review of Electromagnetic and Circuit basics

- Signal Integrity

- Power Integrity

- Electromagnetic Interference and Electromagnetic Compatibility

- Review of SPICE basics

- Lumped models, distributed RLGC, S/Y/Z parameters

- Two conductor transmission line

- 2D Analysis: Multiconductor transmission lines (MTL) extraction

- 2D Analysis: MTL Frequency and Time Domain analysis

- 2D Analysis: MTL Channel simulation

- Power Distribution Network (PDN): Core and IO power

- 2.5D Analysis: Multilayered Finite-Difference Method (M-FDM)

- 2.5D Analysis: Gap and fringe correction

- Decoupling capacitor placement

- Simultaneous switching noise (SSN)

- Partial Element Equivalent Circuit (PEEC) method

- Near and far field radiation

- Comparison of 2D, 2.5D, 3D

- Through-silicon-via modeling

- Stephen H. Hall and Howard. L. Heck: Advanced Signal Integrity for High Speed Designs, 2009, IEEE Computer Society Press

- Howard W. Johnson and Martin Graham: High Speed Signal Propagation: Advanced Black Magic, 2003, Prentice Hall

- Madhavan Swaminathan and Ege Engin: Power Integrity Modeling and Design for Semincorductors and Systems, 2007, Prentice Hall